# СИСТЕМЫ АВТОМАТИЗИРОВАННОГО ПРОЕКТИРОВАНИЯ CAD-SYSTEMS

УДК 621.3.049.771.14

С. В. Гаврилов, д-р техн. наук, зав. отделом, Г. А. Иванова, мл. науч. сотр., e-mail: pirutina\_g@ippm.ru, Д. И. Рыжова, мл. науч. сотр., А. Н. Соловьев, д-р техн. наук, гл. науч. сотр.,

А. Л. Стемпковский, д-р техн. наук, академик РАН, директор, Институт проблем проектирования в микроэлектронике РАН (ИППМ РАН)

# Методы синтеза помехозащищенных комбинационных блоков

Работа посвящена исследованию и разработке методов повышения помехозащищенности комбинационных схем под воздействием различных источников помех и сбоев. Рассмотрены существующие методы повышения надежности работы схем на логическом и системном уровнях. Для обеспечения необходимого уровня помехозащищенности предложен новый подход в проектировании отказоустойчивых комбинационных схем, основанный на синтезе схем защиты в базисе конечных полей Галуа. Особенность предлагаемого подхода заключается в оптимизации схемы контроля за счет выбора схемы коммутации с учетом логических корреляций.

Ключевые слова: помехоустойчивость, упорядоченные диаграммы двоичных решений, поля Галуа

#### Введение

По мере роста степени интеграции и уменьшения технологических размеров возрастает роль повышения надежности и помехоустойчивости проектируемых устройств под воздействием различных источников помех и сбоев: технологических, радиационных, перекрестных помех, деградации во времени, скачков напряжения питания и др. В настоящее время складывается ситуация, когда фактор помехоустойчивости в микроэлектронике становится определяющим условием работоспособности и надежности разрабатываемой электронной аппаратуры. Вместе с тем, несмотря на бурное развитие современных технологий для обеспечения требуемой отказоустойчивости микросистем в основном используют широко известные методы многократного дублирования [1], ведущие часто к неоправданной избыточности. Поэтому актуальной задачей является разработка концептуальных основ и методов построения микросистем, обеспечивающих достижение требуемой надежности функционирования за счет введения управляемой структурной избыточности [2, 3].

## Анализ существующих методов повышения надежности схем на логическом и системном уровнях

Защита схем на логическом уровне проектирования. Одним из подходов для решения задач в области помехозащищенного кодирования является использование линейных и циклических кодов —

кодов Боуза—Чоудхури—Хоквингема (БЧХ-коды) [4, 5]. Такие подходы основаны на использовании алгебры конечных полей [6] и, как правило, используются для защиты систем передачи и хранения данных, но не предназначены для повышения помехозащищенности комбинационных схем.

Альтернативное направление заключается в разработке и исследовании методов маскирования возникающих сбоев (glitch). На уровне транзисторов и p-n-переходов моделируются радиационные эффекты и исследуется реакция логических элементов на такие воздействия. Попадание заряженной частицы приводит к возникновению одиночных эффектов, которые делятся на одиночные ошибки (обратимые) и отказы (необратимые). Здесь и далее будут рассматриваться только методы защиты от обратимых радиационных эффектов.

Обычно одиночные сбои оказывают большее влияние на последовательностные схемы, чем на комбинационную логику, что объясняется наличием трех факторов, которые не позволяют логике стать более чувствительной к одиночным сбоям: логическое маскирование, электрическое маскирование, временное маскирование.

Логическое маскирование состоит в том, что для ошибки в работе схемы одиночный эффект переходной ионизационной реакции (single-event transient) должен распространяться по чувствительному пути от места локализации до триггера-защелки [7].

Из-за электрических свойств вентилей сбой может быть ослаблен или даже полностью маскирован, прежде чем он распространится до триггера-

защелки [8], в этом заключается электрическое маскирование.

При временном маскировании сбой может распространиться в схеме, только если достигнет триггера-защелки и удовлетворит условиям установки и удержания временного сигнала (setup and hold time) [9].

В статье [10] предлагается подход, рассматривающий все типы маскирования одновременно с учетом их совместной зависимости от входных наборов. В работе представлена структура, основанная на ADD (алгебраические диаграммы решений) и BDD (диаграммы двоичных решений) для анализа надежности комбинационных схем:

- чувствительности выхода к сбою;

- влияния отдельных вентилей на отдельные выходы и общую надежность схемы;

- зависимости надежности схемы от длительности сбоя (*glitch*), его амплитуды и входных последовательностей.

Предложенный подход позволяет выбрать технику повышения радиационной стойкости меньшей стоимости за счет подбора размеров вентилей, которые с наибольшей вероятностью вызывают ошибку в работе схемы.

Для оценки вероятности появления ошибок в комбинационной логике в качестве символьных моделей используют диаграммы двоичных решений и алгебраические диаграммы решений. Диаграммы BDD [11, 12] являются эффективным каноническим представлением булевых функций. ADD [13] представляют собой класс символьных моделей и связанных с ними алгоритмов, применяемых не только для Булевой арифметики, но и для многих алгебраических функций. Информация о маскирующих факторах неявно генерируется внутри BDD и ADD и, следовательно, позволяет эффективно распараллеливать вычисление чувствительности выхода к сбоям из-за ошибок в различных внутренних узлах.

Объединенная обработка трех маскирующих факторов необходима по следующим причинам:

- логическое маскирование зависит от входов и топологии схемы, так как чувствительность путей в схеме различается для разных входных векторов;

- электрическое маскирование (затухание сбоя) зависит от вентилей, через которые распространяется сбой, и, таким образом, зависит от логического маскирования;

- вероятность маскирования сбоя зависит от размера сбоя на выходе (т. е. является функцией от начального размера сбоя и затухания на чувствительных путях), а также от размера и относительного времени прибытия сходящихся сбоев, которое влияет на амплитуду/длительность полученного сбоя.

Независимое рассмотрение данных факторов является неверным, так как все они зависят от входов и чувствительных путей.

Если в результате радиационного воздействия на выходе затвора G появился сбой, то он должен удовлетворять условиям установки и удержания триггера. Из этого следует, что существуют ограничения на размер сбоя:

- амплитуда сбоя на выходе F должна быть больше, чем порог переключения триггера-защелки (правильное значение выхода 0) или меньше, чем порог переключения (правильное значение выхода 1);

- продолжительность сбоя на выходе F должна быть больше, чем сумма времен установки и удержания триггера.

Каждую схему анализируют исходя из двух аспектов: надежности выходов при возникновении сбоев в схеме и влияния ошибок на выходы отдельных вентилей. Для каждого выхода  $F_j$ , начальной продолжительности  $d_{init}$  и начальной амплитуды  $a_{init}$  сбоя определяется среднеквадратичная ошибка чувствительности (mean error susceptibility) как вероятность появления ошибки на выходе  $F_j$  в результате возникновения ошибок на внутренних вентилях. Для каждого вентиля  $G_i$ ,  $d_{init}$  и  $a_{init}$  определяются минимальная, максимальная, среднеквадратичная и срединная ошибки отклонения по всем выходам  $F_j$ , на которые влияет сбой, происходящий на выходе вентиля  $G_i$ . Также было получено выражение для оценки числа одиночных ошибок (soft error rate).

**Методы защиты схем на системном уровне.** Для обеспечения сбоеустойчивости схем традиционно применяют три подхода, различающиеся степенью разделения аппаратуры для мажоритарного сравнения [14—16]:

- Интеграция в систему трех синхронных процессоров и устройства сравнения. Достоинство метода — возможно построение системы из стандартных микропроцессоров. Недостаток метода восстановление данных возможно только программным способом, что ведет к большой длительности восстановления.

- Замена каждого триггера на кристалле на схему из трех триггеров с несколькими элементами мажорирования. Достоинство метода возможно автоматическое перепроектирование разработанной БИС и восстановление данных в течение одного такта без вмешательства программного обеспечения. Недостатки метода: не позволяет обнаружить сбои или отказы в комбинационной логике; приводит к снижению быстродействия и существенному увеличению площади кристалла.

- Мажорирование на уровне блоков с потактовым сравнением. Суть метода заключается в том, что весь микропроцессор разбивается на блоки, для каждого блока процессора подбирается наиболее эффективный вариант защиты от сбоев и

метод восстановления данных. Достоинства метода: аппаратные затраты меньшие, чем полное резервирование; возможность восстановления данных без участия программного обеспечения; потери быстродействия и площади на мажорирование меньше, чем для метода резервирования на уровне триггеров. Недостаток метода — большая трудоемкость проектирования по сравнению с полным резервированием или резервированием на уровне триггеров и отсутствие сбоеустойчивости блока при единичном отказе.

#### Синтез схемы защиты

В основе предлагаемой методики лежит новый подход в проектировании отказоустойчивых комбинационных схем, основанный на синтезе схем защиты в базисе конечных полей Галуа (GF) с булевыми коэффициентами. Это дает возможность оптимального сочетания требований минимизации аппаратных затрат и обеспечения требуемого (заданного) уровня отказоустойчивости. В качестве концептуальной основы реализации схемы защиты предложено разделение выходного вектора (результатов работы комбинационной схемы) на подмножества разрешенных и запрещенных кодовых комбинаций, формируемых путем добавления к выходному вектору (имеющему размерность k) проверочного вектора (имеющего размерность r). При этом процедурой формирования проверочного вектора (контрольных разрядов), а также принадлежностью текущего вектора к разрешенным или запрещенным кодовым комбинациям является процедура деления данных кодовых комбинаций на двоичный многочлен G(x), принадлежащий двоичным полям Галуа. В основе данного подхода лежат корректирующие свойства схемы декодирования, позволяющей обнаружить ошибки, возникающие в схеме кодирования. При этом корректирующие способности оцениваются как  $2^{-r}$ .

В рамках данной работы предложен алгоритм структурного синтеза схемы контроля для произвольной комбинационной схемы, зависящий от выбора образующего многочлена G(x), размерности выходного вектора (числа информационных разрядов k) и схемы коммутации, обеспечивающей формирование соответствия между выходом исходной схемы и входом синтезируемой схемы контроля. Структура разработанного алгоритма синтеза описана ниже.

Для описания синтеза схемы контроля будут использоваться следующие обозначения:  $g^r(x)$  — образующий многочлен; r — степень образующего многочлена; y — вектор выходных сигналов комбинационной схемы  $y = y_1, ..., y_i, ..., y_k$ , где k — число выходов; z — вектор выходных сигналов схемы контроля  $z = z_1, ..., z_r$ ; ZM — матрица остатков от деления вектора выходных сигналов на образующий многочлен; y' — вектор, состоящий из вектора

выходных сигналов схемы y и вектора выходов схемы контроля  $z=z_1, ..., z_r; z'$  — вектор выходных сигналов схемы декодирования  $z'=z_1', ..., z_r'$ .

Основная идея предлагаемого метода повышения надежности и отказоустойчивости комбинационных схем состоит в том, чтобы "свернуть" вектор выходных сигналов комбинационной схемы  $y_1, ..., y_i, ..., y_k$ , где k — число выходов, и получить итоговую сигнатурную свертку:  $z_1', ..., z_r'$ , где r — длина (число двоичных разрядов) итоговой сигнатуры.

В качестве примера рассмотрим синтез схемы контроля для случая:

- комбинационная схема с пятью выходами:  $y_1, ..., y_5;$

- в качестве образующего выбран примитивный многочлен  $g^3(x) = x^3 + x + 1$ . При этом остаток от деления y на полином 3-й степени G(x) имеет три разряда и будет обозначаться как  $z_1'$ , ...,  $z_3'$ . Функциональная схема деления вектора, состоящего из вектора выходных сигналов схемы  $y_1, ..., y_j, ..., y_5$  и вектора выходов схемы контроля  $z_1, ..., z_3$ , на образующий многочлен  $g^3(x) = x^3 + x + 1$  и формирования остатков  $z_1'$ , ...,  $z_3'$  показана на рис. 1. При этом знак  $\oplus$  обозначает суммирование

Рассмотрим формирование остатка E1, E2, E3 от деления вектора  $y_1, ..., y_i, ..., y_5, z_1, ..., z_3$  на образующий полином  $g^3(x) = x^3 + x + 1$ . При делении вектора  $y_1, ..., y_i, ..., y_5, z_1, ..., z_3$  на образующий полином формируются следующие промежуточные остатки, представленные на рис. 1:

по модулю 2.

$$A1, A2, A3 \Rightarrow A1 = y_2; A2 = y_1 \oplus y_3; A3 = y_1 \oplus y_4;$$

$B1, B2, B3 \Rightarrow B1 = y_1 \oplus y_3; B2 = y_1 \oplus y_2 \oplus y_4;$

$B3 = y_2 \oplus y_5;$

$C1, C2, C3 \Rightarrow C1 = y_1 \oplus y_2 \oplus y_4;$

$C2 = y_1 \oplus y_2 \oplus y_3 \oplus y_5; C3 = y_1 \oplus y_3 \oplus z_1;$

$D1, D2, D3 \Rightarrow D1 = y_1 \oplus y_2 \oplus y_3 \oplus y_5;$

$D2 = y_2 \oplus y_3 \oplus y_4 \oplus z_1; D3 = y_1 \oplus y_2 \oplus y_4 \oplus z_2;$

$E1, E2, E3 \Rightarrow E1 = y_2 \oplus y_3 \oplus y_4 \oplus z_1;$

$E2 = y_3 \oplus y_4 \oplus y_5 \oplus z_2; E3 = y_1 \oplus y_2 \oplus y_3 \oplus y_5 \oplus z_3.$

$y_1 \quad y_2 \quad y_3 \quad y_4 \quad y_5 \quad z_1 \quad z_2 \quad z_3 \quad \boxed{1011}$

Рис. 1. Функциональная схема деления выходного вектора на образующий полином g(x)

## Суперпозиция с помощью BDD

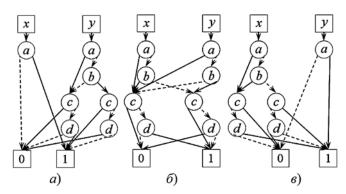

В целях повышения эффективности построения схем защиты разработаны алгоритмы генерации схемы кодирования на основе модифицированных диаграмм двоичных решений (BDD). Стандартная модель BDD расширена дополнительным аппаратом поиска эквивалентных фрагментов на основе сбалансированного двоичного дерева.

Оптимизация для схем кодирования проводится за счет совместной оптимизации дублирующей и кодирующей схем. Одним из путей оптимизации является построение логических функций на основе применения аппарата BDD. Синтез булевых функций в конечных полях Галуа на основе редуцированных диаграмм двоичных решений (ROBDD) позволяет снять существующее в настоящее время ограничение на число входов и выходов проектируемых комбинационных схем. Применение методики ресинтеза полученных решений за счет учета базиса конечных полей Галуа обеспечивает достижение оптимального структурного решения. Использование предлагаемой методики обеспечивает управляемость и предсказуемость процесса проектирования схем при достижении оптимального сочетания заданных требований по отказоустойчивости и минимизации структурных затрат.

Проведенные исследования показали, что на качество результата в терминах занимаемой площади существенное влияние оказывает не только переупорядочивание входов, как в случае стандартной BDD, но и порядок коммутации выходов в схеме кодирования.

## Учет логических корреляций

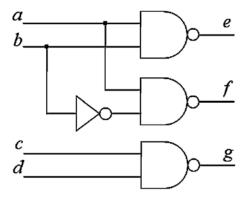

Для выбора оптимального варианта коммутации выходов в схеме кодирования предлагается использовать оценочную функцию, вычисленную на основе расчета взаимных корреляций между выходами [17—21]. Для демонстрации предлагаемого подхода рассмотрим схему, изображенную на рис. 2.

Схема имеет три выхода. Если в качестве образующего полинома выбрать полином второй сте-

Рис. 2. Пример логической схемы с корреляциями между выходами e и f

пени  $(x^2 + x + 1)$ , то кодированная схема будет выглядеть следующим образом:

$$y = x_1 \oplus x_2;$$

$$z = x_2 \oplus x_3$$

,

где ⊕ — операция сложения по модулю два.

Существует N! вариантов коммутации выходов комбинационной схемы и входов схемы кодирования, где N — число выходов. Для комбинационной схемы с тремя выходами число комбинаций равно 6. Если рассмотреть полученную схему кодирования, можно заметить, что от перестановки  $x_1$  и  $x_3$  местами результат не изменится, таким образом, из шести возможных комбинаций остаются три:

1)

$$x_1 = e$$

,  $x_2 = f$ ,  $x_3 = g$ ;

2)

$$x_1 = f$$

,  $x_2 = g$ ,  $x_3 = e$ ;

3)

$$x_1 = g$$

,  $x_2 = e$ ,  $x_3 = f$ .

От выбора коммутирования зависит размер схемы контроля. Варианты BDD-схемы контроля для возможных комбинаций изображены на рис. 3. Из рисунка видно, что в первом и третьем случае число промежуточных узлов равно 4, во втором — 6.

Для выбора оптимального варианта коммутации предлагается учитывать логические корреляции между выходами. В данном примере существуют логические корреляции между выходами е и f. Для снижения структурных затрат при синтезе схемы контроля коррелирующие выходы должны входить в одно выражение. Для поиска логических корреляций между выходами можно воспользоваться методом распространения логических корреляций на основе правила резолюций [22, 23].

Пусть задана пара (V, R), где  $V = \{a, b, ...\}$  — множество булевых переменных, а R — множество булевых соотношений типа A = B; A, B — выражения на множестве V. Множество R преобразуется в одно соотношение g = 0, где g — это ДНФ (дизьюнктивная нормальная форма, т. е. сумма произведений литералов). Для вывода новых ограниче-

Рис. 3. Варианты BDD схемы кодирования

ний предлагается использовать следующее правило резолюции:

$$a \cdot B = 0$$

,  $\overline{a} \cdot C = 0 \mapsto B \cdot C = 0$ ,

где B, C — произведения литералов.

Логические корреляции распространяются вдоль схемы от входов до выходов. Для выбора оптимального варианта коммутации следует учитывать логические корреляции, имеющие в своем составе хотя бы один из выходов. Корреляции разной степени оказывают разное влияние на оптимизацию схемы, поэтому для учета корреляций различных степеней предлагается следующая эвристическая формула:

$$S^*(o_i, o_j) = \sum_{k=1}^{n} n_k(o_i, o_j) \cdot 2^{-k},$$

где  $S*(o_i, o_j)$  — функция учета логических корреляций между i-м и j-м выходами схемы;  $n_k$  — число корреляций k-го порядка.

Наибольший эффект от оптимизации схемы кодирования достигается при условии вхождения в одну формулу выходов схемы, имеющих взаимные корреляции. Для всех выходов дублирующей схемы применяют предложенные методы анализа логических корреляций в цифровой схеме для получения весовых функций. На основе полученных весовых функций выбирается порядок коммутации выходов дублирующей схемы.

#### Заключение

В рамках данной работы рассмотрены существующие методы повышения надежности работы схем на логическом и системном уровнях. Разработан алгоритм синтеза устройства кодирования в базисе полей Галуа. Предложены методы преобразования булевых функций в базисе операций по модулю 2 на основе упорядоченных диаграмм двоичных решений. Предлагается вариант оптимизации схем кодирования за счет выбора варианта коммутирования выходов дубликата основной схемы на основе результатов анализа логических корреляций.

Исследование выполнено за счет гранта Российского научного фонда (проект N 14-19-01036).

#### Список литературы

- 1. **Шишкевич А. А.** Оценка показателей надежности вычислительных устройств с трехкратным мажорированием при отказах и сбоях // Изв. вузов. Электроника. 2013. № 4. С. 84—88.

- 2. Соловьев А. Н., Стемпковский А. Л., Тельпухов Д. В., Соловьев Р. А., Мячиков М. В. Моделирование возникновения неисправностей для оценки надежностных характеристик логических схем // Информационные технологии. 2014. № 11. С. 30—36.

- 3. **Соловьев А. Н., Стемпковский А. Л.** Методы повышения отказоустойчивости работы устройства управления микросис-

темы за счет введения структурной избыточности // Информационные технологии. 2014. № 10. С. 17—22.

- 4. **Сагалович Ю. Л.** Введение в алгебраические коды: учеб. пособие. М.: МФТИ, 2007. 262 с.

- 5. **Poolakkaparambil M., Mathew J.** BCH Code Based Multiple Bit Error Correction in Finite Field Multiplier Circuits // ISQED. 2011. P. 1—6.

- 6. **Poolakkaparambil M., Mathew J., Jabir A.** Multiple Bit Error Tolerant Galois Field Architectures Over GF(2<sup>m</sup>) // Electronics. 2012. P. 3—22.

- 7. **Shivakumar P., Kistler M., Keckler S. W., Burger D.** Modeling the Effect of Technology Trends on the Soft Error Rate of Combinational Logic // Dependable Systems and Networks. 2002. P. 389—398.

- 8. **Wang F., Xie Y., Rajaraman R.** Soft Error Rate Analysis for Combinational Logic Using An Accurate Electrical Masking Model // 20th International Conference on VLSI Design. 2007. P. 165—170.

- 9. **Krishnaswamy S.** On the Role of Timing Masking in Reliable Logic Circuit Design // Design Automation Conference. 2008. P. 924—929.

- 10. **Miskov-Zivanov N., Marculescu D.** MARS-C: Modeling and Reduction of Soft Errors in Combinational Circuits // Design Automation Conference. 2006. P. 767—772.

- 11. **Gavrilov S., Glebov A.** BDD-based Circuit Level Structural Optimization for Digital CMOS // Proc. of MALOPD'99 Workshop, 1999

- 12. **Bryant R. E.** Graph-Based Algorithms for Boolean Function Manipulation // IEEE Trans. on Computers. 1986. P. 677—691.

- 13. **Гаврилов С. В., Гудкова О. Н., Щелоков А. Н.** Логиковременной анализ нанометровых схем на основе интервального подхода // Известия ЮФУ. Технические науки. 2012. № 7 (132). С. 85—91

- 14. РД 134-0139—2005. Аппаратура, приборы, устройства и оборудование космических аппаратов. Методы оценки стойкости к воздействию заряженных частиц космического пространства по одиночным сбоям и отказам. М.: ЦНИИмаш. 2005. 78 с.

- 15. **ГОСТ 27.310—95.** Надежность в технике. Анализ видов последствий и критичности отказов. Основные положения. М.: Изд-во стандартов, 1995. 22 с.

- 16. Соболев С. А. Функциональный метод оценки соответствия аппаратуры требованиям по отказам, вызванным ОЯЧ // Вопросы атомной науки и техники. 2013. № 3. С. 121—132.

- 17. **Гаврилов С. В., Глебов А. Л., Стемпковский А. Л.** Методы логического и логико-временного анализа цифровых КМОП СБИС. М.: Наука, 2007. 223 с.

- 18. **Гаврилов С. В.** Методы анализа логических корреляций для САПР цифровых КМОП СБИС. М.: Техносфера, 2011. 136 с.

- 19. **Gavrilov S. V., Glebov A. L., Soloviev R. A.** etc. Delay Noise Pessimism Reduction by Logic Correlations // In Proc. of ICCAD. 2004. P. 160—167.

- 20. **Гаврилов С. В., Рыжова Д. И., Стемпковский А. Л.** Методы повышения точности оценки пикового тока на логическом уровне на основе анализа логических корреляций // Известия ЮФУ. Технические науки. 2014. № 7. С. 66—75.

- 21. Гаврилов С. В., Гудкова О. Н., Северцев В. Н. Интервальный статический временной анализ КМОП-схем с учетом логических корреляций // Конференция "Проблемы разработки перспективных микро- и наноэлектронных систем 2012": сб. научн. тр. / Под общей ред. А. Л. Стемпковского. 2012. С. 113—118.

- 22. **Glebov A. L., Gavrilov S. V., Blaauw P., Zolotov V., Panda R., Oh C.** False-noise analysis using resolution method // International Symposium on Quality Electronic design, San Jose, CA, Mar. 18—21. 2002. P. 437—442.

- 23. Стемпковский А. Л., Гаврилов С. В., Глебов А. Л. Анализ помехоустойчивости цифровых схем на основе метода резолюций // Электроника, Известия вузов. 2004. № 6. С. 64—71.

S. V. Gavrilov, Head of Department, G. A. Ivanova, Junior Research Scientist, e-mail: pirutina\_g@ippm.ru,

D. I. Ryzhova, Junior Research Scientist, A. N. Soloviev, Chief Researcher,

## A. L. Stempkovskiy, Director

Institute for design problems in microelectronics of Russian Academy of Science

# Methods of Noise Immunity Combinational Blocks Synthesis

This article is dedicated to research and develop methods for increasing the microelectronic circuits' noise immunity under the influence of various sources of failures.

The role of improving the reliability and noise immunity of iesigned devices under the influence of various sources of failures is increases. At present time, the noise immunity factor in microelectronics is becoming critical condition of reliability and working capacity of the developed electronic equipment. One of the key components are combinational circuits. Therefore, research and development of methods for noise immunity improving of microelectronic combinational circuits is actual problem.

The operation of division by the polynomial generator in bimary Galois field is proposed to use to ensure the necessary level of noise immunity (error detection with a predetermined degree of multiplicity) for the synthesis of the coder circuit. Optimization of coder circuit is proposed by choosing variant of outputs commutation basic circuit duplicate based on the results of logical correlations analysis. The existing methods for improving the circuits' reliability on logical and system levels are considered. Synthesis of protection circuits in basis of binary Galois fields is proposed to use to ensure the necessary level of noise immunity for the synthesis of the coder circuit.

Keywords: noise tolerance, binary decision diagram (BDD), Galois field

#### References

- 1. **Shishkevich A. A.** Ocenka pokazatelej nadezhnosti vychislitel'-nyh ustrojstv s trehkratnym mazhorirovaniem pri otkazah i sbojah, *Izvestija vusov. Jelektronika*, 2013, no. 4, pp. 84—88 (in Russian).

- 2. Solov'ev A. N., Stempkovskij A. L., Tel'puhov D. V., Solov'ev R. A., Mjachikov M. V. Modelirovanie vozniknovenija neispravnostej dlja ocenki nadezhnostnyh harakteristik logicheskih shem, *Informacionnye tehnologii*, 2014, no. 11, pp. 30—36 (in Russian).

- 3. **Solov'ev A. N., Stempkovskii A. L.** Metody povyshenija otkazoustojchivosti raboty ustrojstva upravlenija mikrosistemy za schet vvedenija struktumoj izbytochnosti, *Informacionnye tehnologii*, 2014, no. 10, pp. 17—22 (in Russian).

- 4. **Sagalovich Ju. L.** *Vvedenie v algebraicheskie kody: Uchebnoe posobie*, Moscow: MFTI, 2007. 262 p. (in Russian).

- 5. **Poolakkaparambil M., Mathew J.** BCH Code Based Multiple Bit Error Correction in Finite Field Multiplier Circuits, *ISQED*, 2011, pp. 1—6.

- 6. **Poolakkaparambil M., Mathew J., Jabir A.** Multiple Bit Error Tolerant Galois Field Architectures Over GF(2<sup>m</sup>), *Electronics*, 2012, pp. 3—22.

- 7. **Shivakumar P., Kistler M., Keckler S. W., Burger D.** Modeling the Effect of Technology Trends on the Soft Error Rate of Combinational Logic, *Dependable Systems and Networks*, 2002, pp. 389—398.

- 8. **Wang F., Xie Y., Rajaraman R.** Soft Error Rale Analysis for Combinational Logic Using An Accurate Electrical Masking Model. *20th International Conference on VLSI Design*, 2007, pp. 165—170.

- 9. **Krishnaswamy S.** On the Role of Timing Masking ir Reliable Logic Circuit Design, *Design Automation Conference*, 2008, pp. 924—929.

- 10. **Miskov-Zivanov N., Marculescu D.** MARS-C: Modeling and Reduction of Soft Errors in Combinational Circuits, *Design Automation Conference*, 2006, pp. 767—772.

- 11. **Gavrilov S., Glebov A.** BDD-based Circuit Level Structural Optimization for Digital CMOS, *Proc. of MALOPD'99 Workshop*, 1999.

- 12. **Bryant R. E.** Graph-Based Algorithms for Boolean Function Manipulation, *IEEE Trans. on Computers*, 1986, pp. 677—691.

- 13. **Gavrilov S. V., Gudkova O. N., Shhelokov A. N.** Logiko-vremennoj analiz nanometrovyh shem na osnove interval'nogo podhoda,

*Izvestija JuFU. Tehnicheskie nauki*, 2012, no. 7 (132), pp. 85—91 (in Russian).

- 14. **RD 134-0139—2005.** Apparatura, pribory, ustrojstva i oborudovanie kosmicheskih apparatov. Metody ocenki stojkosti k vozdejstviju zarjazhennyh chastic kosmicheskogo prostranstva po odinochnym sbojam i otkazam. Moscow: CNIImash, 2005, 78 p. (in Russian).

- 15. **GOST 27.310—95.** *Nadezhnost' v tehnike. Analiz vidov, posledstyij i kritichnosti otkazov. Osnovnye polozhenija*, Moscow: Izd-vo standartov, 195, 22 p. (in Russian).

- 16. **Sobolev S. A.** Funkcional'nyj metod ocenki sootvetsvija apparatury trebovanijam po otkazam, vyzvannym OJaCh, *Voprosy atomnoj nauki i tehniki*, 2013, no. 3, pp. 121–132 (in Russian).

- 17. **Gavrilov S. V., Glebov A. L., Stempkovskii A. L.** *Metody logicheskogo i logiko-vremennogo analiza cifrovyh KMOP SBIS*, Moscow: Nauka, 2007, 223 p. (in Russian).

- 18. **Gavrilov S. V.** *Metody analiza logicheskih korreljacij dlja SAPR cifrovyh KMOP SBIS*, Moscow: Tehnosfera, 2011. 136 p. (in Russian).

- 19. **Gavrilov S. V., Glebov A. L., Soloviev R. A.** etc. Delay Noise Pessimism Reduction by Logic Correlations. *In Proc. of ICCAD*, 2004, pp. 160—167.

- 20. **Gavriloy S. V., Ryzhova D. I., Stempkovskij A. L.** Metody povyshenija tochnosti ocenki pikovogo toka na logicheskom urovne na osnove analiza logicheskih korreljacij, *Izvestija JuFU. Tehnicheskie nauki*, 2014, no. 7, pp. 66—75 (in Russian).

- 21. **Gavrilov S. V., Gudkova O. N., Severcev V. N.** Interval'nyj staticheskij vremennoj analiz KMOP-shem s uchetom logicheskih korreljacij, *Konferencija "Problemy razrabotki perspektivnyh mikroi nanojelektronnyh sistem 2012"*: sb. nauchn. tr. Pod obshej red. A. L. Stempkovskogo, 2012, pp. 113—118 (in Russian).

- 22. Glebov A. L., Gavrilov S. V., Blaauw D., Zolotov V., Panda R., Oh C. False-noise analysis using resolution method, *International Symposium on Quality Electronic design*, San Jose, CA, Mar. 18—21, 2002, pp. 437—442.

- 23. **Stempkovskij A. L., Gavrilov S. V., Glebov A. L.** Analiz pomehoustojchivosti cifrovyh shem na osnove metoda rezoljucij, *Jelektronika, Izvestija vuzov*, 2004, no. 6, pp. 64—71 (in Russian).